|

| イベント・リポート NO-27

〜EDA業界最大の祭典〜

第49回 Design Automation Conference at San Francisco Moscone Center

20nm以降の設計・検証ツール、FPGAベースのラピッド・プロトタイピング・ボード、新星IPベンダなどに注目

EIS編集部:中村正規 |

|

|

|

|

|

EDA業界の祭典、第49回Design Automation Conference(DAC)が、2012年6月3日から7日まで(展示会は6月4日から6日まで)サンフランシスコのモスコーネ・センターを会場にして開催された。組込みシステムの世界とEDA・LSI設計の世界は、これまで「近くて遠い関係」にあったような気がする。使用される技術用語ひとつとっても、同じ単語でも、お互いの世界では違ったものを連想させることがある。ソフトウェア開発者とハードウェア開発者の文化や常識の違いも長年、良く指摘されてきたことだ。しかし、最近ではシステムの複雑化に伴うシステム・レベル設計の重要性が増し、LSIの設計でも複数のプロセッサを搭載したSoC化の進展で組込みソフトウェアとの緊密な連携や最適化が重要視されるようになり、両者の距離感は以前よりもかなり縮まったように感じる。

|

DAC2012の会場入り口 |

事実、日本でも昨年からEDA関係のイベント、Electric Design & Solution Fair(EDS Fair)が、組込み業界の一大イベントである、組込み総合技術展(Embedded Technology展、略称:ET展)と同時開催されるようになった。長年、ET展と関わってきた筆者は、EDA業界の最大のイベント、Design Automation Conferenceを見学して、EDA業界と組込み業界の距離感を再確認すべく、お寒い懐具合にも拘わらず、サンフランシスコに向かった。以下は、筆者の独断と偏見に満ちたレポートである。

|

|

|

|

■最近のDACと今年の開催規模 |

|

|

| 第49回目を迎えたDACだが、ここ数年は出展社数、来場者数共に減少傾向が続いていたようだ。ここ数年の状況は、EDA業界をまめにフォローしているwebサイト、EDA Expressさんが詳しく説明しているので、こちらを参照して頂きたい。

今年、DACに出展社した企業は主催者発表で約200社ということであったが、1社が複数のブースに出展した場合も重複してカウントされている模様で、EDA Expressの菰田氏が確認した実際の出展社数は174社だったとのこと。筆者は、会場となったモスコーネ・センターには、古くはWESCON Show、近年ではSEMICON WEST、2005年までのEmbedded System Conference(ESC)などで何度も訪れており、馴染みの深い、またダウンタウンタウンに近くてアクセスも便利なので大好きな展示会場のひとつである。

DAC2012は3年ぶりにサンフランシスコのモスコーネ・センターの南館のみを使用して開催されたのだが、かつて南館、北館の双方を使用して開催された以前のDACを知る業界人にとっては、ちょっと寂しい感じがしたようだ。

一方、来場者数について、主催者は前年比16%増の7388名と発表した。その内訳はカンファレンス参加者が1901名、展示会のみの参加者が2783名、展示ブース・スタッフとしての入場者が2704名である。展示ブース・スタッフも参加者数にカウントしているのは、ちょっと驚きでもあるが、この参加者数が示すように展示会場が賑わっていたのは、参加費が無料だった展示会開催初日の6月4日だけで、2日目以降は閑散した展示会であった。

ただしちょっと驚いたのは、米国での組込み系の展示会、ESCに比較して、日本からの来場者が多いことであった。展示会場では、日本語で会話している参加者のグループを頻繁に目撃した。これは、日本におけるEDAツールのユーザーである、大手電子機器、半導体メーカーにはまだ多くの技術者を海外の展示会に派遣できる余裕があると解釈すべきなのであろうか?日本の大手半導体メーカーが28nm以降の微細加工プロセスの開発を断念してファブライト戦略に舵を切り、採算性の悪いSoCビジネスの縮小や他社との事業統合なども視野に入れている状況下においても、日本からDACに参加する人がこれほど多いのは少し意外な感じがした。

|

|

|

|

■賑わう3大EDAベンダのブース |

|

|

|

当然のことながら、この展示会の主役は、Synopsys、Mentor、Cadenceの3大EDAベンダである。このイベントのカンファレンス参加者には、Synopsys社提供のバッグ、Cadence社提供のT-シャツが配られ、来場者バッジのスポンサになったのはMentor Graphics社であった(写真右)。

展示会場で大きなスペースを確保して連日、賑わいを見せていたのも当然ながら、これら3社のブースだった。3社のブースでは、システム・レベル(ESL)の設計・シミュレーション・ツールから、アナログ・ミックスド・シグナル(AMS)のIPとその検証ツール、28nm以降の微細加工プロセスを睨んだ各種のデザイン・ツール、最近話題の3D構造を含む最先端のLSIレイアウト・ツール、熱および電磁界解析ツール、プリント基板設計ツールまでが幅広く展示されていた。個々の製品の詳細については、EDA業界の専門家のレポートなどを参照して欲しい。

|

|

|

|

|

|

| Mentor Graphics のブース |

|

Cadence Design Systemsのブース |

|

|

|

|

■Xilinxが出展、FPGAのベースのプロタイピング・ボード・ベンダも多数出展 |

|

|

|

Xilinxブースにあった

「「WHY ASIC WHEN YOU CAN

GO PROGRAMMABLE ?」の看板

|

驚いたのは、各種の設計、検証、解析ツール、AMSなどのIPベンダなどに混じって、FPGAのトップ・ベンダ、Xilinx社が出展していたことと、同社およびAltera社の最新FPGAを搭載したボード、エミュレータの出展が多かったことだ。Xilinx社のDACへの出展は実に11年ぶりのことだそうだ。システムやLSIの大規模化、複雑化に伴って、ソフトウェア・シミュレーションではなく、システムやSoCの動作機能を初期段階からFPGA上でエミュレーションして確認する、ラピッド・プロトタイピングがFPGAの大容量化と高速化、そして低価格化の進展によって手軽にできる時代が到来したことを示すものであろう。

Xilinxのブースには、「WHY ASIC WHEN YOU CAN GO PROGRAMMABLE ?」と書かれた看板が掲げられ、先ごろ発表された新しい開発環境「VIVADO」のデモが行われていた。同社は、NREが高騰しているASICから、短い開発期間で設計が完了し、設計変更や修正も容易なFPGAへの移行をさらに促進させるための活動を一層、強化しているようだ。

また、ロジック・エミュレータの老舗ともいうべき、Cadence、Mentor、Synopsys、EVEなどの各社は、最新のシステムを使いやすいソフトウェア・ツールとの連携や高性能化などを全面に押し出した展示を行っていた。特に、Synopsysのブースでは、数年前に買収したHAPS社のFPGAベースのエミュレーション・ボードと自社の幅広いEDAツールとの連携を強調していた。

|

|

|

|

|

|

| Synopsys社ブースに展示された

HAPSの最新ボード |

|

かなり大規模なブースで出展したEVE |

|

|

| その他、FPGA搭載のSoC/ IP検証用ボードやシステム製品で出展していたのは、日本でもお馴染みのGiDEL(日本の代理店は立野電脳)、DINI Group(日本の代理店はアプリスター)、BEEcube、(日本の代理店はプロトタイピング・ジャパン)、S2C社(日本の代理店は日本サーキット)、などだ。各社共に、XilinxのVirtex-6および-7、AlteraのStratix-IVおよびVという、40/28nmプロセスの最新FPGAを搭載したボードを中心に展示を行っていた。このうち、中間俊雄という日本人名を持つ人物がCEOを務めるS2C社は、会期前に自社製品のFPGAボードにARM1176およびARM926コアのプロセッサが接続できるオプション・ボードを発表した。ARMコアのプロセッサをFPGAボードに接続可能にしたことで、ARMプロセッサ用ソフトウェアを含むシステム機能の検証がさらに簡単になることが期待できそうだ。

これらFPGAベースの検証、試作用ボードの各社は、用途に合わせた幅広い製品群を、豊富なインターフェースとオプション・ドーター・ボード、効率的な機能分割ソフト、デバッグ・ツールなどと併せて提供している。

筆者は以前から、40nm/28nmプロセスの最先端FPGAはコア電源電圧が1V前後と極端に低く、I/Oも非常に高速化しているため、多様な電圧レベルのI/Oに対応させるために必要な外部接続のDC/DCコンバータ、完全なノイズ対策を実施したボード・パターン設計と実装が非常に重要になると考えていた。各社の担当者に聞いた限り、確かに最先端FPGAの実装は、そう簡単ではないようで、各社はさまざまな苦労と対策をして製品化にこぎつけている模様だ。これらのボードはASIC/SoCのプロトタイプ用途だけでなく、一般のFPGAユーザーにもさらに利用される可能性が高くなると思われる。

|

|

|

|

|

|

| GiDEL社のブース展示 |

|

S2C社のブース |

|

|

| 当方が注目したのは、ドイツから出展してきたProDesign Electronic GmbH、という会社だ。この会社名を聞いたのは初めてなので、スタートアップ企業だと思ったが、すでに30年ほどの社歴を持つ老舗企業だとのこと。これまでは、ハードウェアを中心にしたシステム開発、基板設計・実装などのサービスを提供していたようだ。同社は、proFPGAブランドのFPGA搭載のSoC試作、検証用ボードを外販するビジネスを新たに開始して、今回のDACに乗り込んできたのだ。同社の製品の特徴は同一システム上にAlteraとXilinxのデバイスの双方が搭載可能なことだ。他社の製品はAlteraかXilinxのいずれかのみのデバイスが搭載されているが、ProDesignはベースとなるマザー・ボードにAlteraまたはXilinxのデバイスを搭載したボードを複数、接続できるシステムを提供する。このため、同一システム上にAlteraとXilinxのデバイスをそれぞれ複数個接続することも可能だ。このシステムを使用すれば、両者のデバイスのブロックにデザインをダウンロードして性能を比較することもできるかもしれない。

|

|

|

|

|

|

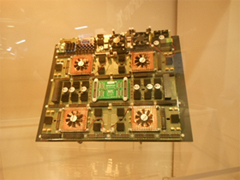

| Pro Design社のproFPGAシステム

(各ボードを接続した状態) |

|

左のシステムに接続されるベースのFPGAボード

左側にあるのが、各ボード間の接続用基板 |

|

|

| 右上の写真を見て解るように、このVirtex-7のベース・ボードには、1個のFPGAに対して周囲に8個ものDC/DCコンバータICが配置、接続されている。ProDesign社は、このproFPGA製品の開発、販売事業を分離、独立させる計画のようで、同社のブースには、北米、アジア地区の代理店募集の看板も立っていた。この製品の販売に関心のある方は、すぐに同社にコンタクトすることをお奨めする。ただし、同社のwebサイトには、このシステムに関する情報がほとんど掲載されていないので、注意が必要だ。

|

これらFPGAベースのエミュレーション・システム、ボード製品の多くは複数のFPGAを搭載しており、大規模なデザインは複数のFPGAに分割されて実装されることになる。ここで重要になるのが、効率的にデザインを分割するソフトウェアである。このイベントには、FPGAベースのプロトタイピング・ボード向けの専用分割ソフトウェア、Wasga Compilerを開発したフランスのFlexras Technologiesという会社も初出展していた。同社のスタッフによれば、Wasga Compilerを採用すれば、このソフトウェアの優れたタイミング・ドリブンな分割機能によって、従来よりも約10倍の動作スピードを実現でき、規模でも10億ゲートまで対応可能と自信を示していた。(写真右上)

同社は、すでにDini Groupのパートナーにもなっているとのこと。日本での販売体制について尋ねるのを失念したのが、私の失敗であった。

FPGA関連のツールでは、三大EDAベンダの他に、シミュレータのALDECや上流設計ツールのBlue Pearl Software社なども元気に出展していたことを付け加えておきたい。

|

|

|

|

■新星IPベンダが数多く出展。またFPGAのIPベンダが新登場 |

|

|

| 1990年代に入ってから半導体業界には、新たに「IPベンダ(プロバイダ)」という新たなビジネス・モデルが本格的に登場したのだが、ARM、MIPS、Tensilica、Rambus、Imagination Technologyなどのような一部の企業を除いて、中小IPベンダのビジネスは困難を極め、その多くは廃業、または大手半導体メーカーやEDAベンダなどに買収、統合される結果となった。しかし、今回のDACでは、本格的なSoC時代の到来と共に、また多くのIPベンダが誕生していることを実感させてくれた。IPベンダとしては確固たる地位を築いたARM社の大きなブースは別格として、目についたのは、AMS関連のIP、例えばPLL/DLLやSERDES関連のIPなどを提供する企業群だ。 AMS関連のIPベンダとして出展していたのは、Analog Bits、Cambridge Analog Technologies (Maxim Integrated Productsの子会社)、Mixel、Silicon Creation、True Circuits, Incなどだ。

|

また、自社開発のIPと中小ベンダのIPを組み合わせて販売するユニークなビジネスを行っているChipStart、Cadenceの下でIPに関するポータル・サイトを運営しているChipEstimateや、同様な機能を提供しているフランスのDesign and Reuseも出展していた。この中で特に目立っていたのがChipEstimateの大きなブースであった。ここでは、IP Talksと呼ばれるIPベンダ、ファンダリ企業などの各社によるプレゼンテーションが連日、休みなく実施されていた。(写真右)

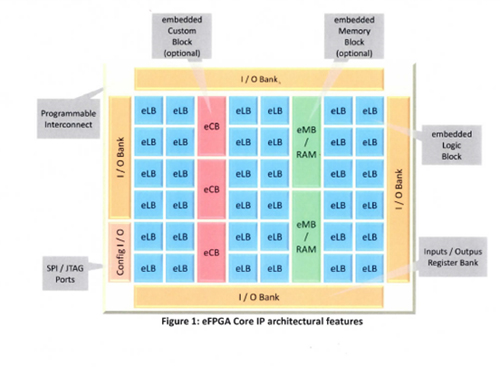

この他に出展していたIPベンダの中で筆者がもっとも注目したのは、フランスから参加してきたMenta(Mentorではない)という、スケーラブルなFPGAのIPコアを開発した企業だ。この会社のeFPGAと呼ばれるIPコアの構造は下図のように、Embedded Logic Block(eLB)のアレイに、RAMまたはEmbedded Memory Blockと用途に応じて性能を最適化するためのEmbedded Custom Block(eCB)をオプションで挿入可能にしてある。これらのブロック間およびI/Oはプログラマブルな配線リソースで接続される。デバイス内部に使用されるコンフィギュレーション・ストレージの素子としては、驚いたことにSRAMだけでなく、NVRAM、Anti-Fuseが使用可能だそうだ。すでに130nm、90nm、40nmプロセスでの評価を終えているとのこと。

同社はこのFPGAコアを合成可能なVHDLまたはVerilogで提供するCore-S、またはハードマクロ版のCore-Hのいずれかで提供する。同社はこのeFPGAに対応した合成後のマッピング、配置配線、およびビット・ストリーム・データ生成の機能をサポートするソフトウェアも提供する。このツールには、何と「Origami」(折り紙)という製品名がつけられていた。

|

|

|

|

| Menta eFPGA IPの内部アーキテクチャ |

|

|

| 上記のように、Menta社のFPGA IPは、内部のコンフィギュレーション・データを保持するためのメモリ素子に選択肢があるものの、アーキテクチャ自体は特に斬新なものではない。

むしろ、搭載されるeCBの回路構成、使用するメモリ素子に応じて内部回路と配置配線を含む設計開発ツールのカスタマイズが必要になることが想像される。

ご承知のように、FPGAの領域ではXilinxとAlteraの2強が市場をほぼ独占しており、新たなファブレスFPGAベンダ、またMenta社のようなFPGA IP企業が食込む余地はないようにも見える。これまでFPGAやダイナミック・コンフィギュラブルな回路技術をIPとしてライセンス販売するビジネスや、ASICの一部にFPGAコアを埋め込んだデバイスのビジネスで成功せずに消えていった企業は何社もある。例を挙げると、LSI Logicのパートナーとして一時は期待を集めたSRAM FPGA IPコアのAdaptive Logic、ASIC+FPGAデバイスのLeopard Logic、コンフィギュラブル・コンピューティングのQuick SilverやIP FLEXなどだ。現在はMicrosewmi社に吸収されたFlashベースのFPGA企業、旧Actelも一時、VariCoreという名前のSRAM FPGAの技術をIPとして外販しようと試みたことがあるが失敗に終わっている。確かに、既存のプロセッサ・ベンダやASSPベンダの中には回路の一部にユーザー・プログラマブルな回路機能を搭載したいと考えているところもあるが、果たしてFPGA IPは市場で受け入れられるのであろうか? 「はい。すでに大手、A社、B社の製品に採用され、アーキテクチャと開発ツールの機能と性能は”折り紙”付きです。」と言える日が来るのか、注目しておきたい。

この他、プロセッサのIPコアでは、気が付いただけでも、以下の企業が出展していたので付け加えておく。

・Cortus S.A. (仏) :マルチ・コア対応の32bit RISC IP

・EnSilica (英):コンフィギュラブル16/32bit 組込み用プロセッサ

・Postage(米):高速セキュア・パケット・プロセッサ

|

|

|

■フランスからの多くの出展企業、日本からの出展は3社のみ |

|

|

EDA業界の中心にいるのは、やはり米国、しかもカリフィルニア州、およびマサチューセッツ州に本社を置く企業群であるのは常識だが、国籍別で云うと米国以外でもっとも多くの出展企業を送り出したのがフランスであった。こちらで数えただけでも、全部で15社が出展していた。 フランス企業の出展社数は多いことは、展示会に来た日本人関係者の中でも話題になっていた。これに対して、我が日本から出展したのは、NEC、JEDAT、TOOLの3社のみで、ちょっと残念で寂しい感じがした。日本の半導体業界が停滞している中、日本のEDAツール・ベンダ、IPベンダ、FPGAボード・ベンダ、デザイン・ハウスの各企業は、こうした世界規模の展示会にもっと積極的に出展して欲しいものだ。

|

|

|

|

|

|

| CyberWorkBenchを売り込んだNEC |

|

レイアウト、解析ツールを展示したJEDAT |

|

|

|

この他、展示会で目を引いたのは、TSMCとGlobal Foundriesの両ファンダリ・メーカーのブースの大きさだった。両社のブースでは、最先端プロセスにおけるデザイン・フローの解説やパートナー各社によるセミナーやデモが実施され、多くの聴衆を集めていた。

|

|

|

|

|

|

| TSMCのブース |

|

Global Foundriesのブース |

|

|

|

この他の海外出展企業の中で、日本からの来場者にも対応できるように日本支社のスタッフや幹部をブースに配置していたのは、気が付いただけでも、Intel(CoFluent部門)、Spring Soft、Forte Design Systems、そしてMentor Graphicsなどの各社であった。

|

|

|

|

|

|

| 日本で顔馴染みの人もいたIntelブース |

|

Forte Design Systemsのブース |

|

|

|

|

■組込みソフトも意識した幅広いカンファレンス・プログラム |

|

|

今回のDACでも、かなり幅広いテーマをカバーしたカンファレンス・プログラムが実施されていた。ARMのCTO、Mike Muller氏を含む計3本の基調講演、パネル討論を含む計54講演のテクニカル・セッション、一日を通じて実施された計6本のチュートリアル、合計8本のワークショップなどである。これらのプログラムの中には、

「Adaptive Computing: When, Where, WHY, How?」

「Probabilistic Embedded Computing」

「Panel: It’s the software, Stupid! Truth or Myth?」

「Heterogeneous Platform Challenges and Opportunities」

「Parallelization and Software Development: Hope, Hype, or Horror」

「PANEL: System Models-Does One Size Fit All?」

など、組込みソフトウェア開発者の関心もそそり、ソフトウェア技術者とハードウェア技術者との接点を探るような内容の講演やパネル討論が行われていた。

当方はARMのMuller氏による基調講演やいくつかのセッションを聴講したのだが、年齢と共に衰退している聴力自体と英語理解力、それに会場の音響設備の悪さがあって必ずしも正確な情報を伝える自信がないので、その詳細については割愛させて頂く。

基調講演で使用されたスライドは、DAC2012の公式サイトでも公開されているので、参考にして欲しい。

なお、次回の記念すべき第50回のDACは、2013年6月2日からテキサス州オースチンで開催される。

最後に展示会2日目に華やかで楽しいパーティに招待して頂いたMentor Graphics Japanの方に心からの謝辞を述べておきたい。

|

|

|

|

|

|

| |

|

|

バックナンバー |

|

|

>>

第49回 Design Automation Conference at San Francisco Moscone Center |

|

|

>>

Embedded System Conference Silicon Valley 2009 No-3 |

|

|

>>

Embedded System Conference Silicon Valley 2009 No-2 |

|

|

>>

Embedded System Conference Silicon Valley 2009 No-1 |

|

|

>>

ZIPC誕生 20周年、第14回ZIPCユーザーズ・カンファレンス |

|

|

>>

Embedded System Conference Silicon Valley 2007 <NO−2> |

|

|

>>

Embedded System Conference Silicon Valley 2007 <NO−1> |

|

|

>>

日本TI 、MSP430: ATC2006 〜アドバンスド・テクニカル・カンファレンス2006〜 |

|

|

>>

ESC

Silicon Valley 2006 その1 |

|

|

>> Digi

Embedded Network Forum 2006 |

|

|

>> Altera

PLD World 2005 東京 |

|

|

>> ETソフトウェアデザインロボコン2005 |

|

|

>> ESC

San Francisco 2005 NO-2 |

|

|

>> ESC

San Francisco 2005 NO-1 |

|

|

>> EDSF

2005 with FPGA/PLD Design Conference |

|

|

>>

SEMICON Japan 2004 |

|

|

>>

ET2004 |

|

|

>>

ALTERA PLD WORLD 2004 |

|

|

>>

ESEC 2004 |

|

|

>> ESC

San Francisco 2004 NO−2 |

|

|

>> ESC

San Francisco 2004 NO−1 |

|

|

>> EDSF2004,

第11回FPGA/PLDコンファレンス |

|

|

>> Semicon

Japan 2003 |