| イベント・リポート NO-14

EDSF 2005 with FPGA/PLD Design

Conference

2005年1月27日-28日 パシフィコ横浜

リポータ : EIS編集部 中村 |

|

|

|

1月27日と28日の両日、Electronic

Design and Solution Fair (EDSF) 2005 と第12回 FPGA/PLD

Design Conferenceが、パシフィコ横浜で開催された。今年のこのイベントで気がついたことなどを例によってとりとめもなくリポートする。

|

|

|

|

|

|

|

| 会場入り口と開会式の模様 |

|

|

基調講演

|

|

|

|

| 基調講演の豊崎氏 |

開催初日の基調講演は、半導体調査会社、iSuppliの日本法人の代表、豊崎禎久氏による「FPGAの将来とストラクチャードASICビジネスのリスク」であった。このイベントには、ザイリンクスとアルテラという2大FPGAベンダが出展していないが、3番手であるアクテルとラティスセミコンダクターの両社が出展していた。また、ここ数年、LSIロジック、NEC、富士通の各社はこのイベントで特にストラクチャードASICのプロモーションに力を注いでいただけに、iSuppli、そして豊崎氏がFPGAとストラクチャードASICの将来性についてどのような見解を示すのかを注目して聴講した。

豊崎氏は2005年の半導体市場をドルベースで4.7%の低成長と予測した上で、FPGAとストラクチャードASICの将来性についての見解を述べた。豊崎氏は「FPGAは消費電力がネックとなって対象となるアプリケーションに一定の制限があるものの、しばらくは安定した成長が期待できる。」と述べた一方で、「プロセスの微細化に伴うNREの高騰、製品ライフサイクルと開発期間の短縮化などの影響でASICの設計件数は減少し、市場規模自体が低成長になっている」と指摘した。そして同氏は、「半導体の主要なアプリケーションである、Digital

TVや携帯電話ではすでに主役がASICからASSPに交替しており、2005年にDigital TVでは90%が、また携帯電話でも61%がASSPで構成されるようになる」と予測した。その上で、「ストラクチャードASICは、セルベースASICの市場の一部は置き換えるが、今後大きな成長は見込めない」という見解を述べた。

これは、このイベントに出展している前記のストラクチャードASICベンダやそれらをサポートしているEDAツール・ベンダにとっては、ちょっと元気を喪失しかねない見解と予測であった。このようなイベントの展示会の基調講演では、出展社や来場者を元気にするスピーチが行われるのが通例なだけに、この講演はちょっと予想外でもあった。

しかし、一方で、豊崎氏の見解を打ち消す動きもあった。各社のストラクチャードASICの合成をサポートしているシンプリシティ社が、この基調講演が行われている時間帯に主要なメディアを集めて富士通、NECエレクトロニクス、富士通の各社と共同で記者会見を行い、「ストラクチャードASICの設計事例が確実に増加している」と発表していた。

果たして、ストラクチャードASICの将来性はどっちの方向なのであろうか? 製品の関係者だけでなく、この行方は大いに気になるところだ。 |

|

展示会場は? |

|

|

今年の展示会参加企業は昨年の104社から119社に増えたとのことであった。確かに、ケイデンス、メンターグラフィックス、シノプシスの3大EDAベンダは例年通り、大きなブースを構えて設計フローの上流から下流までのツール群を展示していた。また、これまで顔を見せていなかった一部の組込み技術関連企業なども新たに出展していたが、他方で昨年まで出展していたアルテラ社などの姿がなく、昨年とはまた少し違った雰囲気を感じさせる展示会となっていた。 |

|

|

新規出展企業 |

|

ARM |

|

|

|

| 青い光が印象的なARM社のブース |

昨年までこのイベントでは見かけなかったARM社のブースがあった。携帯電話などの組込み用プロセッサで高いシェアを誇る同社だが、このイベントでは最新のプロセッサ・コアなどは展示せず、最新の開発環境である、RealViewとデータ・エンジン、Optimo

DEのみを展示していた。 |

|

ガイオテクノロジー |

|

|

|

| 初出展(?)のガイオテクノロジー |

組込みシステムの開発ツールの国内有力ベンダであるガイオテクノロジー社のブースもあった。恐らく、この展示会に同社は初めて参加したものと想像するが、同社のブースでは主力製品である、組込みシステム開発・検証用のシミュレータだけでなく、FPGAをベースにしたSoC開発検証ツール群も示し、同社の幅広い技術力を誇示していた。 |

|

国内半導体ベンダ |

|

富士通 |

|

| 国内の半導体メーカの中でまず目に留まったのは、いつもながらハイセンスなデザインの富士通のブース。 同社のブースは、予想通り前掲のストラクチャードASIC製品、「AccelArray」やIPコアなどを中心にした展示であったが、同社が出資しているベンチャー企業、アイピーフレックス社のダイナミック・リコンフィギュラブル・プロセッサも展示されていた。これは、昨年出展していたアイピーフレックス社が出展していなかったという事情があったのかもしれない。また、富士通のブースで目を惹いたのは、90/65nmプロセス,

300mmウェハーによるファンダリ・サービスのパネルだ。同社はすでにラティスセミコンダクター社からファンダリ・ビジネスを受注したことを発表しており、このビジネスの拡大を狙っているようだ。 |

|

|

|

| ファンダリ・サービスからDAPDNAまでを幅広く展示した富士通ブース |

|

NECエレクトロニクス |

|

|

|

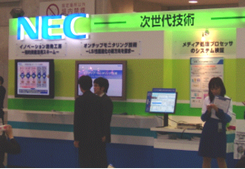

| NECエレクトロニクスのブース |

富士通に比較すれば、NECエレクトロニクスのブースは少し控え目にも見えたが、同社は信号波形をオンチップでモニタリングする技術や、FPGAを活用したエミューレーションとC言語シミュレータを同期させたSoC検証技術などを「次世代技術」のコーナーで紹介していた。 |

勿論、同社が提供するASIC製品群もMIPS、ARMなどプロセッサ・コアを使用して実現したシステムLSIの事例、PCI

Expressを含む幅広いIPコア、開発環境と共に展示されていた。その中で留まったのが、このイベントに合わせて同社が新たに発表した150nmプロセスのCMOSゲートアレイ、CMOS-12Mであった(同発表内容は、こちら)。

|

| |

|

|

|

|

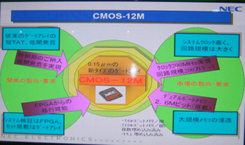

| CMOS-12Mの説明画面 |

NECのゲートアレイについては、0.25ミクロン・プロセスのCMOS-10HD以降、新しい製品発表がなく、今後はセルベースICと新たに開発したストラクチャードASIC、ISSPに力を入れるものと思っていただけに、このゲートアレイの新製品発表にはちょっと驚かされた。 |

|

NECの説明員によれば、低価格で短TATを実現できるゲートアレイの需要はまだ旺盛であり、このCMOS-12Mは200MHz以下の動作周波数で集積度が2百万ゲート以下の低価格が要求される用途を狙った製品であるとのこと。この製品の最低受注数量は1K個となっていて、明らかにFPGAからの置き換えを狙っているように思われるが、自社のストラクチャードASICとの棲み分けと採算性の確保がこのゲートアレイの課題になるかもしれない。 |

|

東芝 |

|

|

|

| MePを中心した展示の東芝ブース |

東芝セミコンダクター社のブースでは、同社の戦略製品のひとつであるコンフィギュラブル・メディア・プロセッサ、MeP関連の展示に加えて、SoCの高性能化、低消費電力化、TAT短縮化などを実現する手法と具体的な成果を示していた。注目されたのは、このイベントの開催前に同社が発表した新しい低消費電力化の手法、「部分fV制御技術」だ。これは、SoC内をブロックごとに最適な動作周波数と動作電圧を設定して消費電力の低減を図る手法で、具体的には低速化できるブロックの動作電圧を下げて電力低減を実現する(詳細は、発表資料を参照)。 |

|

| 海外のFPGA/ASICベンダ |

|

| このEDSFにFPGAカンファレンスが併設されて今年で4年目になると記憶しているが、残念ながら今年の展示会にはザイリンクスとアルテラの2大FPGAメーカが参加していなかった。その替わりというか、ザイリンクスの代理店である菱洋エレクトロニクスと、アルテラの代理店であるアルティマの両社が出展していた。 |

|

|

|

| HardCopy

IIを展示したアルティマ社 |

このうち、アルティマ社のブースでは、アルテラが発表したばかりのストラクチャードASIC、HardCopy

IIを示すパネルが目に留まった。今回発表されたこのHardCopy

IIでは、試作用のFPGAの各論理セルに構成されたロジックが、これと等価なセルに置き換えられてHardCopy

II上に実装され、チップ面積の縮小、コストの低減が実現される。 |

|

|

|

|

| LSIロジック社のプレゼンテーション |

ストラクチャードASICといえば、 LSIロジックもこのイベントには大きなスペースで出展しており、今年になって発表した新製品ファミリ、RapidChip

Intergrator2のプレゼンテーションを行っていた。

この新製品ファミリは1.2Mから5.6Mゲートの範囲をカバーし、最大8Mビットのエンベデッド・マトリックスRAMをサポートしている。

|

PLD/FPGA業界で3番手の地位を争う、アクテルとラティスセミコンダクターの両社が出展していた。アクテル社はこのイベントとほぼ同時に発表したFLASHベースのFPGA、PrpASIC3/Eを中心にした展示を行っていた(ProASIC3記者発表の様子はこちら)。

一方、ラティスは昨年ディジタル信号処理用途などを意識して開発した低価格のSRAMベースFPGA、EC/ECPファミリを中心にした展示を行い、出展者セミナーでもこの製品に関するプレゼンテーションを行っていた

|

|

|

|

|

|

| アクテルのProASIC3の展示

|

|

ラティスセミコンダクター社のブース |

|

|

|

|

| パネル討論会の会場 |

FPGAに関していえば、併設のFPGA/PLDデザイン・カンファレンスのプログラムとして、主要なFPGAベンダとユーザが参加して「本音で語るパネルセッション、FPGAの進む道とユーザの想いのギャップは何か?」というパネル討論会が開催初日の夕方から開催されていた。

こちらのプログラムには、ザイリンクスからの代表もパネリストとして参加しており、夕方にもかわらず、会場は満員に近い状態であった。生憎、最初から最後まで聴講することはできなかったため、「本音」の議論がどこまで行われたまでは確認できなかったが、このようなパネルを毎年実施している関係者の努力にはほんとうに頭が下がる。

|

| ツール・ベンダの展示 |

|

|

|

| HAPS-20の展示 |

毎年、このイベントには多様なツール・ベンダが出展している。昨年はFPGAをベースにしたロジック・エミュレータ・ボード/システムを展示していた企業が多いのが目立ったのだが、今年この種の展示はそれほどほどではなかったような気がした。

そうした中で、プロトタイピング・ジャパン社はスウェーデンのHARDI

Electronics社が提供するASICプロトタイピング・システムの最新製品を展示していた。展示されていた最新製品はザイリンクスのVirtex

II ProをベースにしたHARPS-20で、これはVirtex-II

Proが4個実装されたマザー・ボードを基本にした拡張性に優れたASICの試作用ボードとなっている。

マザー・ボードにはクロック生成回路と拡張用ドーター・ボードや外部デバイスとの接続コネクタが実装されており、FPGAのコンフィギュレーション・データのストレージには大容量のコンパクト・フラッシュが使用できる。

|

|

NTTアドバンステクノロジー社のブースには、SystemCの言語ルールチェッカ&ルール生成ソフトウェア、「accurateC」とSystemC/HDLシミュレーション/ハードウェア・アクセラレータ「iPROVE」が展示されていた。そして、「iPROVE」を活用して実現された例として、株式会社アイシーが開発したHDTV用JPEG2000デコーダのボードも展示されていた。「iPROVE」はHDLソース・レベルでのデバッグ機能を持ち、HDLからC/C++、SystemC言語までのHW/SWの協調シミュレーション環境を構築することができるHDLアクセラレータである。株式会社アイシーでは、HDTVの画像(1,920

x 1,080)を30Hzのフレーム・レートで伸張する放送機器用JPEG2000デコーダを、ザイリンクスのFPGA(Virtex

II)と共にNECのストラクチャードASIC、ISSPを採用して 開発した。同社は、iPROVEを使用することで、複雑な逆ウェーブレット変換などの機能をソフトウェア・シミュレーションでなく、実際の出力画像で短時間で検証できたため、ストラクチャードASICの開発期間を大幅に短縮することができたとのことだった。 |

|

|

|

|

|

| NTTアドバンステクノロジー社の展示パネルとアイシーが開発したJPEG200デココーダ・ボード |

|

|

その他、この展示会ではC言語ベースのSoC設計をサポートする各種のEDAツール群、nmプロセスに対応したレイアウト・ツール、アサーション・ベースの形式検証ツールなどの出展が目立っていた。 |

|

この展示会でも「お美しいキャンペーン・ガール」が登場してアンケートの記入依頼などを行ってはいたが、展示ブースの高さが制限されているせいか、各社のブースは他の展示会に比較して少し地味な印象を受けた。なお、来場者の総数は、主催者発表で1万1千名以上だったようだ。 |

|

| |

| バックナンバー |

>>

SEMICON Japan 2004 |

|

|

>> ET2004 |

|

|

>> ALTERA

PLD WORLD 2004 |

|

|

>> ESEC

2004 |

|

|

>> ESC

San Francisco 2004 NO−2 |

|

|

>> ESC

San Francisco 2004 NO−1 |

|

|

>> EDSF2004,

第11回FPGA/PLDコンファレンス |

|

|

>> Semicon

Japan 2003 |