| ƒCƒxƒ“ƒgپEƒٹƒ|پ[ƒg NO-18

Altera PLD World 2005 “Œ‹پ@10Œژ21“ْ

“Œ‹چ‘چغƒtƒHپ[ƒ‰ƒ€

ƒٹƒ|پ[ƒ^ پF EIS•زڈW•”پ@’†‘؛ |

|

|

|

|

|

| ‰ïڈê“à‚إ‚جƒvƒŒƒ[ƒ“ƒeپ[ƒVƒ‡ƒ“ |

“ْ–{‚جPLD/FPGAژsڈê‚إƒgƒbƒvƒVƒFƒA‚ج’nˆت‚ًˆغژ‚µ‚ؤ‚¢‚éƒAƒ‹ƒeƒ‰ژذ‚ھچP—ل‚جƒvƒ‰ƒCƒxپ[ƒgپEƒVƒ‡پ[پAپuPLD

WORLD 2005پv‚ًٹJچأ‚µ‚½پB“Œ‹‚ج‰ïڈê‚حپA‚±‚ê‚ـ‚إ‚ئ“¯‚¶—Lٹy’¬‚ج“Œ‹چ‘چغƒtƒHپ[ƒ‰ƒ€پB“ْ–{‚جFPGAژsڈê‚إƒgƒbƒvƒVƒFƒA‚ًŒض‚éƒAƒ‹ƒeƒ‰‚¾‚¯‚ةچ،”N‚جƒCƒxƒ“ƒg‚ة‚à‘½‚‚ج‹Zڈpژز‚ھ—ˆڈꂵ‚ؤ‚¢‚½پB |

|

ƒQƒXƒgچu‰‰‚ةگ¼کa•Fژپ‚ھ“oڈê |

|

| “–“ْ‚جƒvƒچƒOƒ‰ƒ€‚حپA“¯ژذ‚جPLD

WORLDگê—pƒTƒCƒg‚إٹm”F‚إ‚«‚é‚ھپAچ،”N‚جٹî’²چu‰‰‚ة‚ح“¯ژذ‚جƒ}پ[ƒPƒeƒBƒ“ƒO’S“–ڈم‹‰•›ژذ’·‚جJordan

S. Plofskyژپ‚ھپAƒQƒXƒgچu‰‰‚ة‚ح‘O“ْŒoƒGƒŒƒNƒgƒچƒjƒNƒX•زڈW’·‚جگَŒ©’¼ژ÷ژپ‚ئڈ®”üٹw‰€‘هٹw‹³ژِ‚جگ¼کa•Fژپ‚ھ“oڈꂵ‚½پBگ¶‘پA‚ا‚جچu‰‰‚à’®چu‚·‚邱‚ئ‚ح‚إ‚«‚ب‚©‚ء‚½‚ھپAƒAƒ‹ƒeƒ‰‚جƒCƒxƒ“ƒg‚جƒQƒXƒgپEƒXƒsپ[ƒJپ[‚ئ‚µ‚ؤŒ³ƒAƒXƒLپ[‚جگ¼کa•Fژپ‚ھ“oڈꂵ‚½‚ج‚حپA‘½‚‚جگl‚ة‚ئ‚ء‚ؤڈپXˆسٹO‚¾‚ء‚½‚©‚à‚µ‚ê‚ب‚¢پB“¯ژپ‚جچu‰‰ƒ^ƒCƒgƒ‹‚حپuƒIپ[ƒvƒ“پEƒ\پ[ƒXپEƒnپ[ƒhƒEƒFƒAپv‚ئ‚¢‚¤‚à‚جپBژہ‚حپAگ¼کa•Fژپ‚ئFPGA‚جٹضŒW‚حگ[‚¢پBکb‚ح“¯ژپ‚ھƒAƒXƒLپ[‚جژذ’·‚ً–±‚ك‚ؤ‚¢‚½ژ‘م‚ة‘k‚é‚ھپAƒAƒXƒLپ[‚ح90”N‘مڈ‰“ھ‚ةƒNƒچƒXƒ|ƒCƒ“ƒgپEƒ\ƒٹƒ…پ[ƒVƒ‡ƒ“ƒY‚ئ‚¢‚¤پAƒtƒ@ƒCƒ“پEƒOƒŒƒCƒ“چ\‘¢‚جƒAƒ“ƒ`پEƒqƒ…پ[ƒYFPGA‚ًٹJ”‚µ‚ؤ‚¢‚½ƒAƒپƒٹƒJ‚جƒxƒ“ƒ`ƒƒپ[ٹé‹ئ‚ة‘½ٹz‚جڈoژ‘‚ًچs‚¢پA“ْ–{‚ج“ْ—§گ»چىڈٹپiŒ»پAƒ‹ƒlƒTƒXƒeƒNƒmƒچƒWپj‚ًƒtƒ@ƒu‚ة‚µ‚ؤپAFPGAژsڈê‚ة‘إ‚ء‚ؤڈo‚éŒv‰و‚ً—§‚ؤ‚½پBژc”O‚ب‚ھ‚çپA‚±‚جŒv‰و‚ح‚³‚ـ‚´‚ـ‚ب——R‚إ”j’]‚µ‚ؤ‚µ‚ـ‚ء‚½‚ھپAگ¼ژپ‚ح‚»‚ج“–ژ‚©‚çFPGA‚جڈ«—ˆگ«‚ً—\Œ©‚·‚é‚ئ‹¤‚ةپAFPGAƒrƒWƒlƒX‚ج“ءˆظگ«‚ً‘جŒ±‚µ‚½ˆêگl‚¾پBگ¼ژپ‚ھƒQƒXƒgپEƒXƒsپ[ƒJپ[‚ة“oڈꂵ‚½‚à‚¤‚ذ‚ئ‚آ——R‚ئ‚µ‚ؤچl‚¦‚ç‚ê‚é‚ج‚ھپAپuMSXƒpƒ\ƒRƒ“پv‚ج•œچڈƒuپ[ƒ€‚©‚à‚µ‚ê‚ب‚¢پB‚²ڈ³’m‚ج‚و‚¤‚ةپA‚Wƒrƒbƒg‚ج‰ئ’ë—pƒpƒ\ƒRƒ“پAMSX‚ً80”N‘م”¼‚خ‚ة’ٌڈ¥‚µ‚½‚ج‚حپAگ¼ژپ‚جƒAƒXƒLپ[‚ئƒ}ƒCƒNƒچƒ\ƒtƒg‚إ‚ ‚ء‚½پBچً”N‚جAlteraپ@PLDپ@World‚إ‚حMSX‚جƒnپ[ƒhƒEƒFƒA‹@”\‚ًƒAƒ‹ƒeƒ‰‚جCycloneƒfƒoƒCƒXپA1Œآ‚إژہŒ»‚µ‚½پu1ƒ`ƒbƒvMSXپv‚ھ”•\‚³‚êپA’چ–ع‚ًڈW‚ك‚ؤ‚¢‚½پB‚»‚جŒمپAƒAƒXƒLپ[‚حپuMSX‰i‹v•غ‘¶”إپv‚ب‚éژGژڈ‚ًٹ§چs‚µپAڈH—tŒ´‚إMSX

WORLD‚ئ‚¢‚¤ƒCƒxƒ“ƒg‚ـ‚إٹJچأ‚µ‚½پB‚ ‚ج—L–¼‚ب‘هŒ^Œfژ¦”إ‚إ‚àMSXƒlƒ^‚حچ،‚إ‚àگ·‚èڈم‚ھ‚ء‚ؤ‚¢‚é‚و‚¤‚¾پB |

|

| گVگ»•iپAStratix II GX ‚ئQuartus

II version 5.1 |

|

|

|

| ‹Lژز‰ïŒ©ڈê‚ةŒf‚°‚ç‚ꂽStratix

II GX‚جƒpƒlƒ‹پ@ |

چً”N‚جPLD WORLD 2004‚إ‚حپAƒAƒ‹ƒeƒ‰‚ھ90nmƒvƒچƒZƒX‚ًژg—p‚µ‚ؤٹJ”‚µ‚½گVگ»•iپAStratixپACycloneپAMAXپAHardCopyƒtƒ@ƒ~ƒٹ‚جپuIIƒVƒٹپ[ƒYپv‚ھ‘µ‚¢پA’چ–عڈ¤•i‚ھ–ع”’‰ں‚µ‚جٹ´‚ھ‚ ‚ء‚½‚ھپAچ،”N‚حŒمڈq‚جچ‚‘¬ƒVƒٹƒAƒ‹پEƒVƒٹƒAƒ‹پEƒCƒ“ƒ^ƒtƒFپ[ƒX“à‘ ‚جStratix

II GX‚ج‚ف‚ھ‚±‚جƒCƒxƒ“ƒg‚ة‚ظ‚عچ‡‚ي‚¹‚½Œ`‚إ‹Lژز”•\‚³‚ꂽپi”•\ژ‘—؟‚ح‚±‚؟‚çپjپB

ƒAƒ‹ƒeƒ‰‚ة‚ئ‚ء‚ؤپAچ،”N‚حچً”N”•\‚µ‚½پuIIƒVƒٹپ[ƒYپv‚جƒfƒUƒCƒ“پEƒCƒ“‚ًگi‚ك‚éژٹْ‚ة“–‚èپAگV‚½‚بƒAپ[ƒLƒeƒNƒ`ƒƒ‚جگVگ»•i”•\‚ح—ˆ”Nˆبچ~‚ة‚ب‚é‚ئژv‚ي‚ê‚éپB |

|

‚³‚ؤپAچ،‰ٌ”•\‚³‚ꂽStratix II GX‚¾‚ھپAڈ]—ˆ‚جStratix

GX‚ة”نٹr‚µ‚ؤƒTƒ|پ[ƒg‚³‚ê‚éچإچ‚ƒfپ[ƒ^پEƒŒپ[ƒg‚ھ–ٌ2”{‚ج6.375Gbps‚ـ‚إپAڈWگد“x‚àڈ]—ˆ–ٌ‚R”{‚ة‘ٹ“–‚·‚éچإ‘ه130K

LEگ”‚ـ‚إ‚ةٹg’£‚³‚ê‚ؤ‚¢‚éپB“à‘ ‚³‚ê‚éƒgƒ‰ƒ“ƒVپ[ƒo‚جƒ`ƒƒƒlƒ‹گ”‚حپAچإ‘ه‚إ20ƒ`ƒƒƒlƒ‹‚ـ‚إپB‚±‚جƒCƒxƒ“ƒg‚ج‘O“ْ‚جچs‚ي‚ꂽ‹Lژز”•\‚ة‚¨‚¯‚éƒAƒ‹ƒeƒ‰‚جگà–¾‚ة‚و‚ê‚خپAStratix

II GX‚إƒTƒ|پ[ƒg‚³‚ê‚éƒfپ[ƒ^پEƒŒپ[ƒg‚ح‚à‚ء‚ئ‚à‘½‚‚جƒAƒvƒٹƒPپ[ƒVƒ‡ƒ“‚إژg—p‚³‚êپA‚©‚آƒfƒoƒCƒXپEƒRƒXƒg‚جچإ“K‰»‚ھ‰آ”\‚ة‚ب‚é622Mbps‚©‚ç6.375Gbps‚ج”حˆح‚ةگف’肳‚êپA‚ ‚¦‚ؤOC-192‚ب‚ا‚ج‚و‚¤‚ب‚³‚ç‚ةچ‚‘¬‚ج•Wڈ€‹Kٹi‚جƒTƒ|پ[ƒg‚حƒRƒXƒg‚â•à—¯‚ـ‚è‚ب‚ا‚ًچl—¶‚µ‚ؤ”ً‚¯‚½‚ئ‚ج‚±‚ئ‚إ‚ ‚ء‚½پiƒUƒCƒٹƒ“ƒNƒX‚حپAVirtex-4

FX‚إ10.315Gbps‚ـ‚إ‚ج“]‘—ƒŒپ[ƒg‚ًƒTƒ|پ[ƒg‚·‚é‚ئ”•\‚µ‚ؤ‚¢‚éپjپBStratix II GX‚ة“à‘ ‚³‚ê‚ؤ‚¢‚éگê—p‚جچ‚‘¬ƒgƒ‰ƒ“ƒVپ[ƒo‚حپAچإ‘ه500%پA3ƒ^ƒbƒv‚جƒvƒٹƒGƒ“ƒtƒ@ƒVƒX‹@”\پi‘—گM‘¤پj‚ئچإ‘ه17dbپA4’i‚جƒCƒRƒ‰ƒCƒU‚ة‚و‚èپAƒVƒOƒiƒ‹پEƒCƒ“ƒeƒBƒOƒٹƒeƒB‚جٹm•غ‚µپAƒgپ[ƒ^ƒ‹پEƒWƒbƒ^‚ً’لŒ¸‚·‚éپBƒAƒ‹ƒeƒ‰‚ھ“ء‚ة‹’²‚µ‚ؤ‚¢‚½‚ج‚حپAStratix

II GXƒgƒ‰ƒ“ƒVپ[ƒo‚ج’لڈء”ï“d—ح“ءگ«‚إ‚ ‚ء‚½پBƒAƒ‹ƒeƒ‰‚ة‚و‚ê‚خپAStratix II GX‚جƒgƒ‰ƒ“پ[ƒo“–‚è‚جڈء”ï“d—ح‚حپA6.375Gbps“®چىژ‚إ225mW‚ئپA‹£چ‡•i‚إ‚ ‚éƒUƒCƒٹƒ“ƒNƒX‚جVirtex-4

FX‚ئ”نٹr‚·‚é‚ئ‚Q•ھ‚ج‚Pˆب‰؛‚ة‚ب‚é‚ئگà–¾‚µ‚ؤ‚¢‚½پBپ@ƒAƒ‹ƒeƒ‰‚إ‚حپA‚±‚جStratix II GX‚جƒfƒUƒCƒ“‚ً“¯ژ‚ة”•\‚µ‚½ٹJ”ƒ\ƒtƒgƒEƒFƒAپAQuartus

II‚جگVƒoپ[ƒWƒ‡ƒ“پAv.5.1‚إƒTƒ|پ[ƒg‚·‚é‚ئ‹¤‚ةپAچ،ŒمپA•]‰؟ƒ{پ[ƒh‚ب‚ا‚à’ٌ‹ں‚·‚é—\’è‚إ‚ ‚éپBƒfƒoƒCƒX‚ج‹ں‹‹‚حپA—ˆ”N‚ج‘و‚Pژl”¼ٹْ‚©‚çٹJژn‚³‚ê‚é—\’è‚ئ‚ب‚ء‚ؤ‚¢‚éپB |

|

ƒAƒ‹ƒeƒ‰‚حپAStratix II GX‚ئ“¯ژ‚ةٹJ”ƒcپ[ƒ‹پAQuartus

II‚جچإگV”إپAƒoپ[ƒWƒ‡ƒ“5.1‚à”•\‚µ‚½پBپi”•\ژ‘—؟‚حپA‚±‚؟‚çپj

چ،“x‚جگVƒoپ[ƒWƒ‡ƒ“‚إ‚حپAڈم‹L‚جStratix II GX‚ھƒTƒ|پ[ƒg‚³‚ê‚é‚ئ‹¤‚ةپAƒfƒoƒCƒX‚جڈء”ï“d—ح‚ًگ„’肨‚و‚رژ©“®“I‚ةچإ“K‰»‚·‚éپAگV‚µ‚¢PowerPlay‹@”\‚ھ’ٌ‹ں‚³‚ê‚éپB‚±‚جPowerPlay‹@”\‚ًٹˆ—p‚·‚邱‚ئ‚إپAƒoپ[ƒWƒ‡ƒ“5.0‚جڈêچ‡‚و‚è‚àپAƒ_ƒCƒiƒ~ƒbƒNڈء”ï“d—ح‚ً•½‹د‚إ20پ“پAStratix

II ƒfƒoƒCƒX‚ة‚¨‚¢‚ؤ‚حچإ‘ه60پ“‚ـ‚إچيŒ¸‚إ‚«‚é‚ئ‚ج‚±‚ئ‚¾پB‚ـ‚½پAگV‚½‚ة’ٌ‹ں‚³‚ê‚éپuƒCƒ“ƒNƒٹƒپƒ“ƒ^ƒ‹پEƒRƒ“ƒpƒCƒ‹پEƒ{ƒgƒ€ƒAƒbƒvپEƒtƒچپ[پv‚ة‚و‚èپA•،گ”‚جگفŒvژز‚ھŒآ•ت‚ج‰ٌکH‹@”\‚ً“ئژ©‚ةٹJ”پAچإ“K‰»‚µپA‚»‚جŒم‚ة‘S‘ج‚جƒfƒUƒCƒ“‚ضٹب’P‚ة“چ‡‚إ‚«‚é‚و‚¤‚ة‚ب‚éپB‚ـ‚½پA‚±‚ج‹@”\‚ة‚و‚èپA“ء’èƒuƒچƒbƒN‚جگ«”\‚ًˆغژ‚µ‚ب‚ھ‚瑼‚جƒuƒچƒbƒN‚ًچإ“K‰»‚·‚邱‚ئ‚ھ‰آ”\‚ة‚ب‚é‚ئگà–¾‚µ‚ؤ‚¢‚éپB |

|

ƒAƒ‹ƒeƒ‰‚ة‚و‚éƒvƒŒƒ[ƒ“ƒeپ[ƒVƒ‡ƒ“ |

|

| ALTERA PLD

WORLD‚ج‰ïڈê“à‚إ‚حپAچإگVگ»•i‚ج‰ًگàپAƒVƒXƒeƒ€پEƒRƒXƒg‚ج’لŒ¸چôپAFPGA‚جڈء”ï“d—ح‘خچôپAƒWƒbƒ^‚ج•ھگح‚ئ‘خچôپAHardCopy

ƒXƒgƒ‰ƒNƒ`ƒƒپ[ƒhASIC‚ج—ک“_پAƒfƒBƒWƒ^ƒ‹گMچ†ڈˆ——pƒfƒUƒCƒ“پEƒcپ[ƒ‹‚ب‚ا‚ةٹض‚·‚éƒvƒŒƒ[ƒ“ƒeپ[ƒVƒ‡ƒ“‚ھچs‚ي‚ê‚ؤ‚¢‚½پB

‚±‚ج‚¤‚؟پAڈ¬گ¶‚ھ’®چu‚µ‚½ƒWƒbƒ^‚ج•ھگح‚ئ‘خچô‚ةٹض‚·‚éƒvƒŒƒ[ƒ“‚ح”ٌڈي‚ة‚ي‚©‚è‚â‚·‚پA‚ئ‚ؤ‚àژQچl‚ة‚ب‚ء‚½پB‚±‚ê‚ـ‚إPLD/FPGA‚جƒxƒ“ƒ_‚ةچفگذ‚µ‚ؤ‚¢‚é‚ج‚حپuƒfƒBƒWƒ^ƒ‹پv‚ج‹Zڈpژز‚خ‚©‚è‚إپAGbpsƒŒپ[ƒg‚جچ‚‘¬ƒVƒٹƒAƒ‹’تگM‚ھ’¼–ت‚·‚éپuƒAƒiƒچƒOپv—جˆو‚ج–â‘è‚ة‚àگ¸’ت‚µ‚½‹Zڈpژز‚حڈ‚ب‚©‚ء‚½‚و‚¤‚ةژv‚¤‚ھپA“ْ–{ƒAƒ‹ƒeƒ‰‚إ‚حچ‚‘¬ƒCƒ“ƒ^ƒtƒFپ[ƒX‚إگ¶‚¶‚éڈ”–â‘è‚ة‚à‘خ‰‚إ‚«‚é‹Zڈpژز‚ً‘‹‚µ‚ؤ‚¢‚é‚ئ‚ج‚±‚ئ‚¾پi“ْŒGژذ’·’kپjپB

‘S”ت“I‚ة‚حپAژ©ژذ‚جƒfƒoƒCƒX‚âٹJ”ٹآ‹«‚ةٹض‚·‚éƒvƒŒƒ[ƒ“ƒeپ[ƒVƒ‡ƒ“‚ھ‘½‚©‚ء‚½‚ھپAچ،”N‚àƒIƒٹƒ“ƒpƒXƒپƒfƒCƒJƒ‹ƒVƒXƒeƒ€پiٹ”پj‚ب‚اپAƒ†پ[ƒU‚ة‚و‚éگفŒvژ–—ل‚ج”•\‚à‚ ‚ء‚½‚ج‚حٹ´گS‚µ‚½پB |

|

| ƒTپ[ƒhپEƒpپ[ƒeƒB‚ج“Wژ¦ |

|

| ‰ïڈê‚ة‚حپA‘½گ”‚جƒTپ[ƒhپEƒpپ[ƒeƒBپEƒxƒ“ƒ_‚ئ“ْ–{ƒAƒ‹ƒeƒ‰‚ج”ج”„‘م—“X‚ھƒuپ[ƒX‚ًچ\‚¦‚ؤƒAƒ‹ƒeƒ‰پEƒfƒoƒCƒX‚ة‘خ‚·‚éچإگV‚جƒTƒ|پ[ƒgگ»•i‚âƒTپ[ƒrƒX‚ً—ˆڈê‚ة‘i‚¦‚ؤ‚¢‚½پB‚»‚ê‚ç‚ج’†‚إ–ع‚ة—¯‚ـ‚ء‚½ڈo“Wژذ‚âگ»•i‚ًڈذ‰î‚·‚éپB |

|

‚Pƒ`ƒbƒvMSX |

|

|

|

| MSXƒAƒ\ƒVƒGپ[ƒVƒ‡ƒ“‚جƒuپ[ƒX |

‚ـ‚¸پA–ع‚ة“ü‚ء‚½‚ج‚حپAMSXƒAƒ\ƒVƒGپ[ƒVƒ‡ƒ“‚ھ“Wژ¦‚µ‚½پu1ƒ`ƒbƒvMSXپvپBMSX‚جƒnپ[ƒhƒEƒFƒA‹@”\‚ً1Œآ‚جFPGA‚إژہŒ»‚µ‚½‚à‚ج‚إپA“–ڈ‰‚ح‚±‚جگ»•i‚ًƒAƒXƒLپ[‚ھ”ج”„‚ًŒv‰و‚µ‚ؤ‚¢‚½‚ھ’†ژ~‚ة‚ب‚èپAMSXƒAƒ\ƒVƒGپ[ƒVƒ‡ƒ“‚ھڈ¤ژذ‚ب‚ا“ء’è‚ج”جکH‚ً’ت‚¶‚ؤ”ج”„‚·‚é—\’肾‚»‚¤‚¾پB |

|

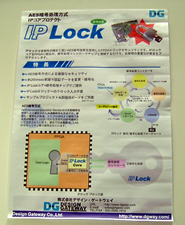

IP Lock |

|

| ƒAƒ‹ƒeƒ‰‚ھ”F’肵‚½ƒfƒUƒCƒ“پEƒRƒ“ƒTƒ‹ƒ^ƒ“ƒgپEƒpپ[ƒgƒiپiACAPپj‚إ‚ ‚èپAJTAGƒ|پ[ƒg‚©‚çFPGA‚ًƒRƒ“ƒtƒBƒMƒ…ƒŒپ[ƒVƒ‡ƒ“‚·‚郂ƒWƒ…پ[ƒ‹‚ب‚ا‚ً’ٌ‹ں‚µ‚ؤ‚¢‚éپiٹ”پjƒfƒUƒCƒ“پEƒQپ[ƒgƒEƒFƒCژذ‚جƒuپ[ƒX‚إ‚حپAAESˆأچ†‚ًژg—p‚µ‚ؤƒfƒUƒCƒ“پEƒfپ[ƒ^‚ً•غŒى‚·‚邽‚ك‚جIP‚ھ”•\‚³‚ê‚ؤ‚¢‚½پB‚±‚جIP‚ح200msژüٹْ‚إƒfƒUƒCƒ“پEƒfپ[ƒ^‚ًˆأچ†‰»پA•دچX‚·‚é‹@”\‚ً—L‚µ‚ؤ‚¢‚é‚ئ‚ج‚±‚ئ‚¾‚ء‚½پB

|

|

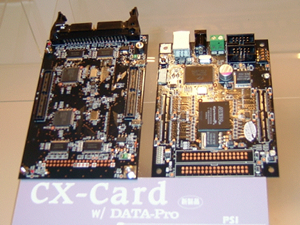

USBƒCƒ“ƒ^ƒtƒFپ[ƒX‚جFPGAƒ{پ[ƒh |

|

| ’·–ى‚جƒvƒ‰ƒCƒ€ƒVƒXƒeƒ€ƒYژذ‚حپACyclone

FPGA‚ئUSBƒCƒ“ƒ^ƒtƒFپ[ƒX‚ً“‹چع‚µ‚½پA‘gچ‚فپ^ژژچىٹJ”—p‚جƒ{پ[ƒhپACX-Card‚جٹg’£ƒIƒvƒVƒ‡ƒ“پEƒ{پ[ƒh‚ئ‚µ‚ؤٹJ”‚µ‚½گVگ»•iپAData-Pro‚ً“Wژ¦‚µ‚ؤ‚¢‚½پB‚±‚جData-Pro‚ة‚ح144ƒsƒ“‚جSO-DIM‚lƒ\ƒPƒbƒg‚ھ“‹چع‚³‚ê‚ؤ‚¨‚èپA512MB‚ـ‚إƒپƒ‚ƒٹ‚ًژہ‘•پAگ§Œن‚إ‚«‚邽‚كپACX-Card‚ئ‘g‚فچ‡‚ي‚¹‚邱‚ئ‚إپA‘ه—ت‚جƒfپ[ƒ^‚ًژو‚舵‚¤—p“r‚ض‚ج‘خ‰‚ً‰آ”\‚ة‚µ‚½پB |

|

|

|

|

|

|

| ƒfƒUƒCƒ“پEƒQپ[ƒgƒEƒFƒC‚ج

IP Lock‚ج“Wژ¦ƒ|ƒXƒ^پ[ |

|

ƒvƒ‰ƒCƒ€ƒVƒXƒeƒ€ƒY‚جCX-Card‚ئData-Pro |

|

|

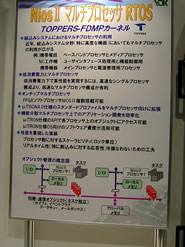

ƒ}ƒ‹ƒ`پEƒ\ƒtƒgپEƒvƒچƒZƒbƒTپEƒRƒA‘خ‰‚جRTOSƒJپ[ƒlƒ‹ |

|

|

|

| TOPPERS-FDMP‚جƒpƒlƒ‹ |

iTRONژd—l‚جRTOS‚ًƒIپ[ƒvƒ“پEƒ\پ[ƒX‰»‚µ‚ؤ’ٌ‹ں‚·‚éٹˆ“®‚ًچs‚ء‚ؤ‚¢‚éTOPPERS

PROJECT‚ج’†گS“I‚بƒپƒ“ƒoپ[‚إ‚à‚ ‚éپiٹ”پjƒڈƒCƒfپ[ƒPپ[‚جYDKƒeƒNƒmƒچƒWپ[ƒY‚جƒuپ[ƒX‚إ‚حپATOPPERS-FDMPƒJپ[ƒlƒ‹‚جƒfƒ‚‚ًچs‚ء‚ؤ‚¢‚½پB

‚±‚جTOPPERS-FDMPƒJپ[ƒlƒ‹‚حپAƒAƒ‹ƒeƒ‰‚جNios IIƒ\ƒtƒgپEƒRƒAپEƒvƒچƒZƒbƒT‚ً•،گ”Œآژہ‘•‚µ‚½ƒVƒXƒeƒ€‚ًƒTƒ|پ[ƒg‚µ‚½iTRONژd—l‚جƒ}ƒ‹ƒ`پEƒvƒچƒZƒbƒT‘خ‰‚جRTOSƒJپ[ƒlƒ‹‚إپAچ،”N‚جڈt‚ة”•\‚³‚ê‚ؤ‚¢‚éپB“¯ژذ‚ح‚±‚جƒ}ƒ‹ƒ`پEƒvƒچƒZƒbƒTپEƒRƒA‘خ‰‚جRTOS‚ًٹـ‚قƒVƒXƒeƒ€پEƒfƒUƒCƒ“‚جژَ‘ُ‚ًچs‚¤‚ئ‹¤‚ةپANios

‘خ‰‚جEthernet MAC‚جIPپAIPv6‘خ‰‚جITRON TCP/IPƒvƒچƒgƒRƒ‹ƒXƒ^ƒbƒN‚ب‚ا‚ج”ج”„‚àچs‚ء‚ؤ‚¢‚éپB

|

|

|

|

| DSPƒxپ[ƒX‚جƒVƒXƒeƒ€پEƒ{پ[ƒh |

|

|

|

| ƒCƒXƒ‰ƒGƒ‹‚ً‹’“_‚µ‚½ƒ{پ[ƒhپEƒxƒ“ƒ_پAGiDEL

Ltd‚حپADSPپA‘ه—e—ت‚جDRAMپA•،گ”‚جچ‚ڈWگدFPGA‚ً“‹چع‚µ‚½ƒ{پ[ƒh‚ً“Wژ¦‚µ‚ؤ‚¢‚½پB‚±‚جƒ{پ[ƒh‚حپADSP‚ئFPGA‚ج“‹چعگ”پADRAM‚ج—e—ت‚ًٹg’£‚إ‚«‚é‚و‚¤‚ةگفŒv‚³‚ê‚ؤ‚¨‚èپADSPپiTIژذ‚جTMC320C6414پjƒxپ[ƒX‚ة‚µ‚½‘g‚فچ‚فƒVƒXƒeƒ€‚جژژچىٹJ”‚âƒVƒXƒeƒ€LSI‚جƒGƒ~ƒ…ƒŒپ[ƒVƒ‡ƒ“‚ًˆسژ¯‚µ‚½گ»•i‚ج‚و‚¤‚¾پBTI‚جDSP‚ئچ‚‘¬ڈوژZٹي‚ً“à‘ ‚µ‚½Stratix‚ھ“¯ˆêƒ{پ[ƒhڈم‚ةژہ‘•‚³‚ê‚ؤ‚¢‚邽‚كپAچL”حˆح‚بگMچ†ڈˆ—ƒAƒvƒٹƒPپ[ƒVƒ‡ƒ“‚ة‘خ‰‚إ‚«‚é‚ئژv‚ي‚ê‚éپBژتگ^‚جPROCSuperStar‚ة‚حپAStratix

80‚ھ‚RŒآپA“‹چع‚³‚ê‚ؤ‚¨‚èپAچإ‘ه21Œآ‚ـ‚إ‚جژہ‘•‚ھ‰آ”\‚ة‚ب‚ء‚ؤ‚¢‚邽‚كپA‚©‚ب‚è‘ه‹K–ح‚بƒVƒXƒeƒ€‚ة‚à‘خ‰‚إ‚«‚éپB‚ـ‚½پAHW‚ئSW‚جٹJ”‚ًƒVƒXƒeƒ€پEƒŒƒxƒ‹‚©‚çƒTƒ|پ[ƒg‚·‚éƒcپ[ƒ‹‚à•¹‚¹‚ؤ’ٌ‹ں‚µ‚ؤ‚¢‚éپB“¯ژذ‚ج“ْ–{‚ج‘م—“X‚ح—§–ى“d”]پB |

|

|

|

| GiDELژذ‚جPROCSuperStar |

|

|

| گV‚µ‚¢‘م—“X |

|

| چ،‰ٌ‚جALTERA PLD WORLD‚جڈo“Wژز‚ة‚حگV‚µ‚¢ٹç‚ھ‚ ‚ء‚½پBگو‚²‚ëپA“ْ–{‚إ‚جگV‚½‚ب‘م—“X‚ة‚ب‚ء‚½ٹغ•¶‚ئ‹kƒeƒNƒgƒچƒ“‚ج—¼ژذ‚¾پBƒAƒ‹ƒeƒ‰‚ح“ْ–{‚ج”ج”„‘م—“X‚ً•دچX‚¹‚¸پA’·‚¢ٹشپAPALTEK‚ئƒAƒ‹ƒeƒBƒ}‚ج“ٌژذ‚ةˆث‘¶‚µ‚ؤ‚«‚½پBƒ‰ƒCƒoƒ‹‚جƒUƒCƒٹƒ“ƒNƒX‚ھ“ْ–{‚ج‘م—“X‚ً‰½“x‚©•دچX‚µ‚½‚èپA’ا‰ء‚µ‚ؤ‚«‚½‚ج‚ئ‚ح‚ ‚éˆس–،‚إ‘خڈئ“I‚¾‚ء‚½پB‚±‚±‚ة‚«‚ؤپA“ْ–{ƒAƒ‹ƒeƒ‰‚ھگV‚½‚ة”ج”„‘م—“X‚ً‚Qژذ’ا‰ء‚µ‚½”wŒi‚ة‚حپAگ»•iƒ‰ƒCƒ“‚ئƒ†پ[ƒU‚جچL‚ھ‚肾‚¯‚إ‚ب‚پAƒUƒCƒٹƒ“ƒNƒX‚ب‚ا‘¼‚جFPGAƒxƒ“ƒ_‚جچUگ¨‚ھ‚ ‚ء‚½‚ئچl‚¦‚ç‚ê‚éپBگV‚½‚ب‘م—“X‚ة‰ء‚ي‚ء‚½ٹغ•¶‚حپAˆب‘OپAƒUƒCƒٹƒ“ƒNƒX‚ج‘م—“X‚¾‚ء‚½‚±‚ئ‚à‚ ‚èپAFPGAƒrƒWƒlƒX‚ة‚آ‚¢‚ؤ‚جŒoŒ±‚ًژ‚ء‚ؤ‚¢‚éپBˆê•û‚ج‹kƒeƒNƒgƒچƒ“‚حپAƒAƒ‹ƒeƒBƒ}‚ئ“¯‚¶ƒ}ƒNƒjƒJژP‰؛‚جٹé‹ئ‚إ‚ ‚èپAŒo‰cٹ²•”‚ة‚ح‚©‚آ‚ؤƒAƒ‹ƒeƒBƒ}‚إƒAƒ‹ƒeƒ‰پEƒrƒWƒlƒX‚ج’†گS“I‘¶چف‚¾‚ء‚½گl‚à‚¢‚éپB“¯ژذ‚ح‹ك‚پAژذ–¼‚ًƒGƒXƒeƒBƒi‚ة•دچX‚·‚邱‚ئ‚à”•\‚µ‚ؤ‚¢‚éپB |

|

|

|

| گV‚µ‚¢‘م—“XپAٹغ•¶‚جƒuپ[ƒX |

|

|

| ET2005 |

|

| چ،‰ٌ‚جALTERA PLD WORLD‚ةچs‚¯‚ب‚©‚ء‚½•û‚حپA”ج”„‘م—“X‚جƒAƒ‹ƒeƒBƒ}‚ھ“ْ–{ƒAƒ‹ƒeƒ‰‚ئ‹¤‚ة11Œژ16“ْ‚©‚çƒpƒVƒtƒBƒR‰،•l‚إٹJچأ‚³‚ê‚éEmbedded

Technologyپi‘gچ‚ف‘چچ‡‹Zڈp“Wپj‚ةڈo“W‚·‚é‚ج‚إپA‚»‚؟‚ç–K–â‚·‚é‚ئ—ا‚¢پB11Œژ17“ْ‚ة‚حپAFPGA

TRACK‚ئ‚¢‚¤–³—؟‚ج‹ZڈpƒZƒ~ƒiپ[‚ة‚¨‚¢‚ؤ“ْ–{ƒAƒ‹ƒeƒ‰‚ج‹´‹l‰pژ،ژپ‚ة‚و‚é‚Q‚آ‚جچu‰‰‚à—\’肳‚ê‚ؤ‚¢‚éپB |

|

پiڈI‚ي‚èپj |

|

| |

| ƒoƒbƒNƒiƒ“ƒoپ[ |

>> ETƒ\ƒtƒgƒEƒFƒAƒfƒUƒCƒ“ƒچƒ{ƒRƒ“2005 |

|

|

>> ESC San

Francisco 2005 NO-2 |

|

|

>> ESC San

Francisco 2005 NO-1 |

|

|

>> EDSF

2005 with FPGA/PLD Design Conference |

|

|

>> SEMICON

Japan 2004 |

|

|

>> ET2004 |

|

|

>> ALTERA

PLD WORLD 2004 |

|

|

>> ESEC

2004 |

|

|

>> ESC

San Francisco 2004 NOپ|2 |

|

|

>> ESC

San Francisco 2004 NOپ|1 |

|

|

>> EDSF2004,

‘و11‰ٌFPGA/PLDƒRƒ“ƒtƒ@ƒŒƒ“ƒX |

|

|

>> Semicon

Japan 2003 |