SOLUTION

OTSLなど4社が世界初となる次世代プロセッサIP(RISC-V)向けの包括的なソフト開発環境の実現に成功

2023.4.27 7:43 pm

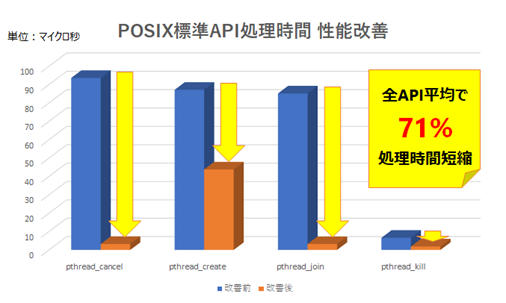

マルチコア対応高性能ランタイム環境(RTE)において処理時間を平均71%短縮

NEDOは「高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発」(以下、本事業)に取り組んでおり、その一環で、このたび株式会社OTSLは、株式会社エヌエスアイテクス、京都マイクロコンピュータ株式会社、イーソル株式会社と共同で、次世代プロセッサIP(RISC-V)向けエッジコンピューティングのための包括的なソフト開発環境の実現に成功しました。

さまざまな機能が混在するヘテロジニアスな環境下でのRISC-V向けオペレーティングシステム(OS)、各種並列化フレームワーク、コンパイラ基盤、並列プログラム処理のための開発ツールを組み合わせた包括的なソフト開発環境を実現したのは世界初となります。このヘテロジニアスなマルチコア対応の高性能ランタイム環境(RTE)で、車載、産業機器で広く使われているポータブル・オペレーティングシステム・インターフェース(POSIX)標準のアプリケーション・プログラミング・インターフェース(API)における処理時間を従来比平均71%短縮するなど、高い性能と開発支援機能が備わっていることを確認しました。

これにより、人工知能(AI)をエッジシステムのRISC-Vアーキテクチャーで利用する際に必要となる、高速かつ高効率・低消費電力なRTEと開発ツールで構成されるRISC-V開発環境エコシステムが実現可能となり、国内でのRISC-Vアーキテクチャーのさらなる利用拡大が期待できます。

1. 概要

IoT社会の到来により急増した情報の高度な利活用を促進するには、ネットワークの末端(エッジ)で中心的な情報処理を行うエッジコンピューティングなど処理の分散化を実現することが不可欠です。また、半導体の開発指標となってきたムーアの法則の終焉が叫ばれ、既存技術の延長は限界を迎えつつある中、著しく増加するデータの処理電力を劇的に低減できるような新しい原理での技術の実現が求められています。

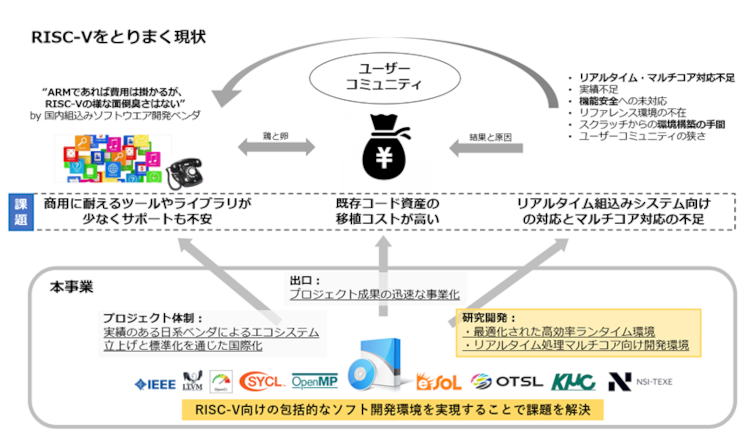

こうした中、オープンな次世代プロセッサIP(RISC-V[リスクファイブ])アーキテクチャーは、拡張性、カスタマイズ性、モジュール性に優れ、さまざまなワークロードやアプリケーション向けに容易に最適化することが可能であるため、急成長が見込まれています。

しかし、これを搭載したエッジシステムで活用できるAIを開発するためには、より高速・高効率・低消費電力のランタイム環境(RTE)や、コンパイラ基盤、並列プログラム処理のための開発ツールが必要です。これに対して現在、それぞれ個別の製品やサービスはあるものの、開発者にとって包括的で使いやすい環境がなく、RISC-Vアーキテクチャーの持つポテンシャルを十分に生かしきれないことが利用拡大に向けた課題でした。

このような背景の下、NEDO(国立研究開発法人新エネルギー・産業技術総合開発機構)は本事業※で、特に組み込みシステムで競争力を発揮するために重要となる処理効率・リアルタイム性を確保することや、国内ユーザーが必要としているより高速かつ高効率で低消費電力のランタイム環境(RTE)や、コンパイラ基盤、並列プログラム処理のための開発ツールを実現するため、既存のRISC-Vの開発環境をベースにRISC-Vコア向けにOSや開発ツールの開発と実証評価を行ってきました。

このたび、本事業の一環で株式会社OTSLは、株式会社エヌエスアイテクス、京都マイクロコンピュータ株式会社、イーソル株式会社と共同で機能検証や性能評価を行い、各社の強みを融合したRISC-V向けエッジコンピューティングの包括的なソフト開発環境の実現に成功しました。

さまざまな機能が混在するヘテロジニアスな環境下でRISC-V向けのOS、各種並列化フレームワーク、コンパイラ基盤、並列プログラム処理のための開発ツールを組み合わせた包括的なソフト開発環境の実現は世界でも初となります。このマルチコア対応の高性能RTEにおいて、車載、産業機器で広く使われているポータブル・オペレーティングシステム・インターフェース(POSIX)標準のアプリケーション・プログラミング・インターフェース(API)処理における処理時間を従来比平均71%短縮するなど、高い性能と開発支援機能が備わっていることを確認しました。

これにより、本事業で目指してきたAIをエッジシステムのRISC-Vアーキテクチャーで利用する際に必要な高速・高効率・低消費電力なRTEと開発ツールを包括的に提供することで、国内におけるRISC-V対応のソフト開発が活性化し、RISC-Vアーキテクチャーのさらなる利用拡大が期待できます。このようにRISC-Vベンダーのビジネス拡大(市場拡大)に寄与することで好循環(RISC-Vエコシステム)が見込めます。

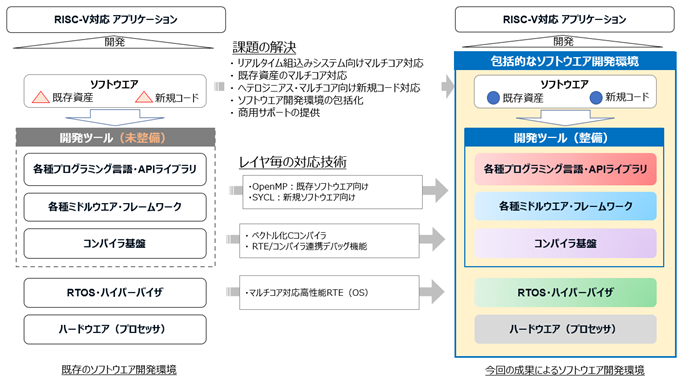

本プロジェクトで包括化されたRTEと開発ツールの構成を図1に示します。

2. 今回の成果

従来からRISC-Vを利用可能なツールや開発環境は存在していましたが、ソフトを開発する際には、開発者自身がそれらを組み合わせて利用する必要がありました。それらは必ずしも最適に連携したものではなかったためスムーズな開発とRISC-Vの持つポテンシャルを十分に引き出すことが難しく、また余分な手間も発生していました。今回4社の強みを融合し、新たなソフト開発環境として包括的に提供することにより、RISC-V向けエッジコンピューティングのための最適なソフト環境を用意できました。

また、AIをエッジシステムで利用するようなハイパフォーマンスコンピューティングを視野に入れ、以下三つの目標を掲げて研究開発を進めてきました。

(1) 計算量の多いAI処理、信号処理、制御を含めた非対称用途への適用とレガシーコードの混在に対応した高性能でリアルタイムなRTEおよびプログラミング環境の実現

(2) AI処理などの電力効率を1桁高めるためにRISC-V Vector extension(RVV)に対応

(3) 日本が強みとする車載や産業機器をはじめとする高信頼系システムへの適用

その結果、以下の性能向上、改善を実現しました。

・RISC-Vに最適化されたマルチコア対応の高性能RTEの設計・開発において、目標としていた水準を大きく上回る従来比平均71%の処理時間短縮を達成しました(図3)。

・セキュアオープンアーキテクチャ向け並列化対応開発環境の設計・開発において、従来に比べて25%の並列化効率の改善とソフトウエア開発ターン・アラウンド・タイム(TAT)の50%改善を実現しました。

・セキュアオープンアーキテクチャ向けベクトル化Cコンパイラの設計・開発において、自動的に適切なRVV命令を生成するコンパイラ基盤を開発し、直接イントリンシック関数を記述した場合と同等機能でかつ目標値である80%以上の性能と10倍以上の生産性改善を達成しました。

・セキュアオープンアーキテクチャ対応RTEのオープンソース化実証および対応評価環境の設計・開発で、ツールチェインと連携可能なRTEを開発し、ロウ レベル バーチャルマシン(LLVM)との連携部分の無駄を排除することでリアルタイムOS(RTOS)の起動やタスク切り替えなどで20%以上の時間短縮を実現しました。

※ 高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発

事業名 : 革新的AIエッジコンピューティング技術の開発/セキュアオープンアーキテクチャ向けコンパイラバックエンドおよび対応ランタイム環境の設計・開発

事業期間: 2020年度~2022年度

事業概要: https://www.nedo.go.jp/activities/ZZJP_100123.html