SOLUTION

Microchip社、よりシンプルでスマートな設計を実現する、プログラマブル ロジック機能統合型デバイスを発表

2026.4.22 6:55 pm

-2026.4.22発表-

モータ制御、産業用オートメーション、車載安全アプリケーション等のタイミング クリティカルなシステムを設計するエンジニアは、レイテンシやソフトウェア実行の予測不能性の課題にしばしば直面しています。

こうした課題に、マルチチップ設計によるコスト増や複雑化を招く事なく対処するため、Microchip Technology Incorporatedは、CLB(構成可能なロジックブロック) ベースMCU(マイクロコントローラ)のポートフォリオを拡充した事を発表しました。PIC16F13276ファミリとPIC18-Q35ファミリは、CPLD(コンプレックス プログラマブル ロジックデバイス)に匹敵するプログラマブル ロジックとMCUが低消費電力のシングルデバイスに統合された製品です。

Microchip社のCLBは、ロジック機能をソフトウェアではなく専用ハードウェアで実装可能にする事で、マルチタスク処理を簡素化するように設計されています。ソフトウェアのみのMCUソリューションやCPLDとMCUを個別に実装する場合と比較して、消費電力を低減し、システム動作の予測可能性を高め、スループットを向上させる事ができます。

新しいデバイスファミリは、電源投入時またはリセット時にCLBを自動的にロードするオプションを備えており、CPUとは独立してロジックを初期化できます。これにより、機能安全、産業用、車載システムで求められる予測可能な起動時挙動に対応します。

PIC16F13276ファミリは32個、PIC18-Q35ファミリは128個のロジック エレメントを搭載しており、1つのチップ上に組み込み制御に加えて、並列的かつ決定論的なロジックを実装できます。個別のCPLDとMCUを使う設計をこの統合的なアプローチに置き換える事で、BOM(部品表)と基板専有面積を削減でき、システム全体のコストと複雑さも低減できます。

Microchip社MCU business unit担当副社長のGreg Robinsonは次のように述べています。

「Microchip社の新製品開発は競合他社に追随するためではなく、実際の設計課題を効率的に解決する事を目的としています。これら2つのファミリは、低消費電力で費用対効果に優れたマイクロコントローラ上にCPLDのような機能を実現できるため、エンジニアはプログラマブル ロジックを設計に手軽に取り入れられるようになります」

これらのデバイスは既存のPIC16およびPIC18設計とドロップイン互換であるため、システム全体の設計を変更する事なくハードウェア ベースのロジックを導入できます。さらに、PDID(プログラム/デバッグ インターフェイス無効化)による耐タンパ保護機能を備え、不正アクセスや悪意ある改ざんから設計を保護します。

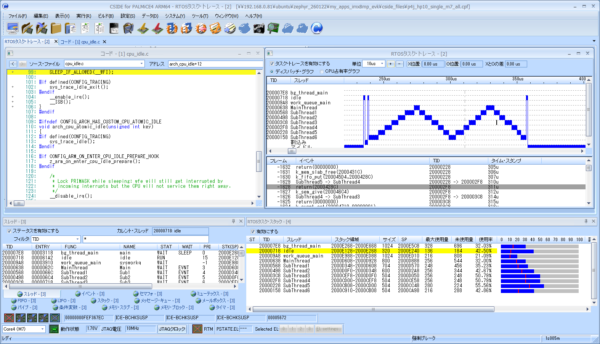

Microchip社のCLBは、ハードウェア ベースのタイミングパスにより、ソフトウェア ベースのシステムにおけるタイミングの課題に対処します。また、CLBタイミング解析ツールを使う事で、信号遅延、クリティカルパス、潜在的なタイミングリスクを設計サイクルの早い段階で特定できます。タイミングの問題を事前に検証する事で、デバッグ時間を短縮できます。

Microchip社のCLB対応MCUポートフォリオ詳細

https://www.microchip.com/en-us/products/microcontrollers/8-bit-mcus/peripherals/system-flexibility/clb

Microchip Technology社

https://www.microchip.com